**SAPIENZA**

UNIVERSITÀ DI ROMA

# Controllori a logica programmabile (PLC)

Automazione

Vincenzo Suraci

## STRUTTURA DEL NUCLEO TEMATICO

1. CONTROLLORI LOGICI

2. RETI LOGICHE E PLC

3. STRUTTURA DEI PLC

- MEMORIA

- SEZIONE DI I/O

4. PROGRAMMAZIONE DEI PLC

# CONTROLLORI LOGICI

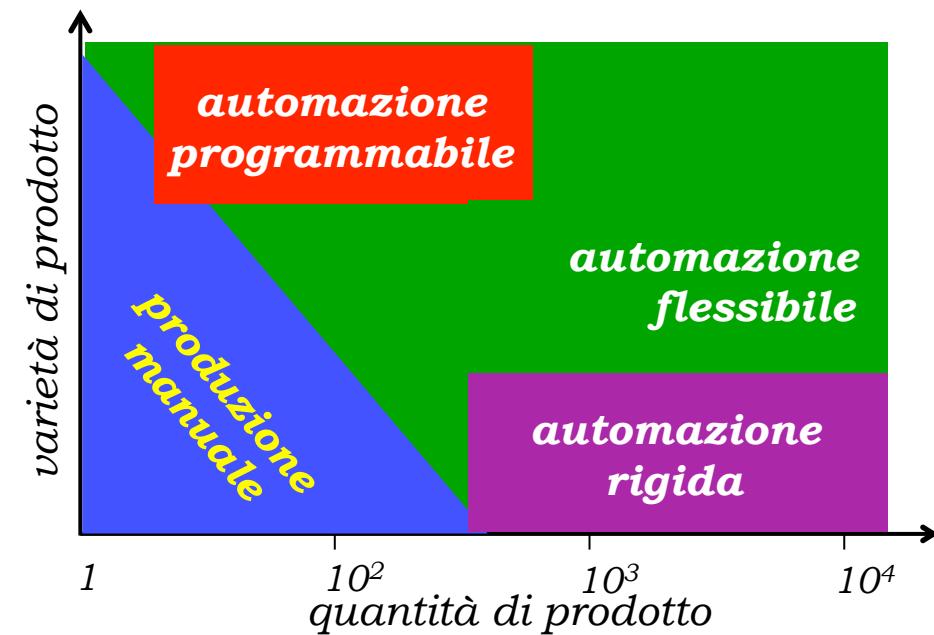

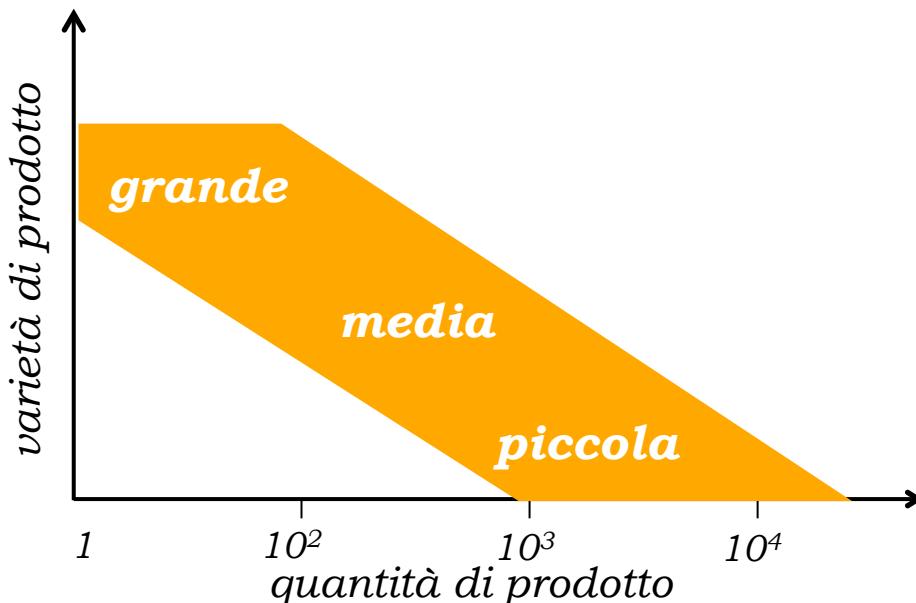

## ETEROGENEITÀ E QUANTITÀ DI PRODOTTO

- La **produttività** di un sistema controllato dipende dalla **QUANTITÀ** del prodotto realizzata per unità di tempo, che a sua volta è collegata alla **ETEROGENEITÀ** della produzione del sistema controllato nonché alle modalità con cui è stata resa operativa l'automazione.

## ORIGINI DEI CONTROLLORI LOGICI

- I controllori logici furono realizzati per poter fare evolvere la **PRODUZIONE DI SERIE DA MANUALE AD AUTOMATIZZATA**

- La loro realizzazione dipendeva dalle tecnologie disponibili

- Attualmente, con lo sviluppo dei circuiti elettronici a larga integrazione e dei dispositivi di elaborazione digitale di tipo dedicato, i controllori logici sono realizzati con **TECNOLOGIE ELETTRONICHE**

## ORIGINI DEI CONTROLLORI LOGICI

In base alla realizzazione i **controllori logici** possono essere di tipo:

- **CABLATO** quando l'elaborazione della logica di controllo è ottenuta impiegando **RELÈ E PORTE LOGICHE** opportunamente connesse (**RETI LOGICHE**)

- **PROGRAMMABILE** quando l'elaborazione è effettuata sulla base di un **ALGORITMO DI CONTROLLO** espresso tramite un **PROGRAMMA (PLC)**

La differenza sostanziale fra rete logica e controllore a logica programmabile sta nella **RAPIDITÀ DI ELABORAZIONE** e nella **FLESSIBILITÀ DI PROGRAMMAZIONE**

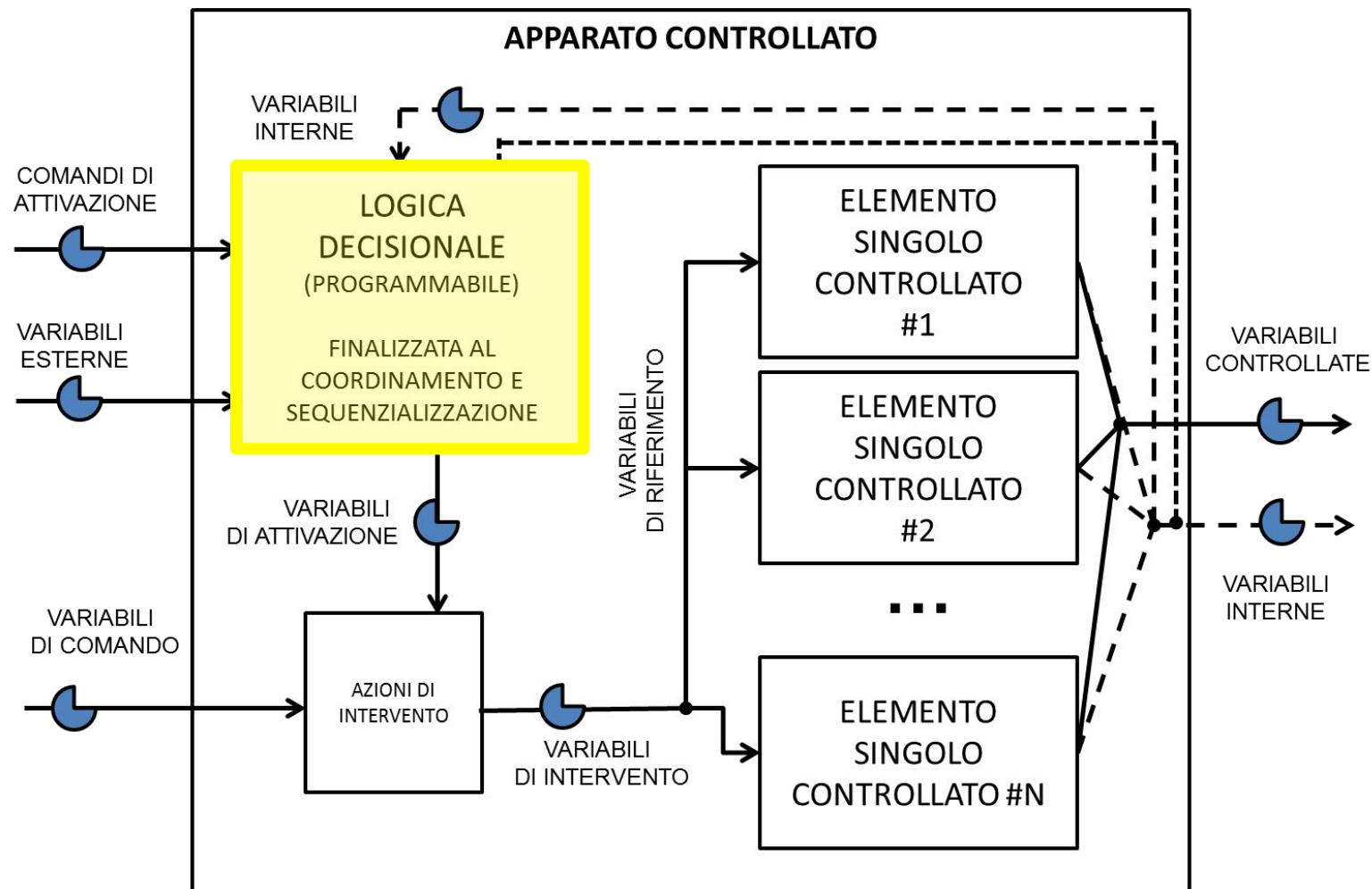

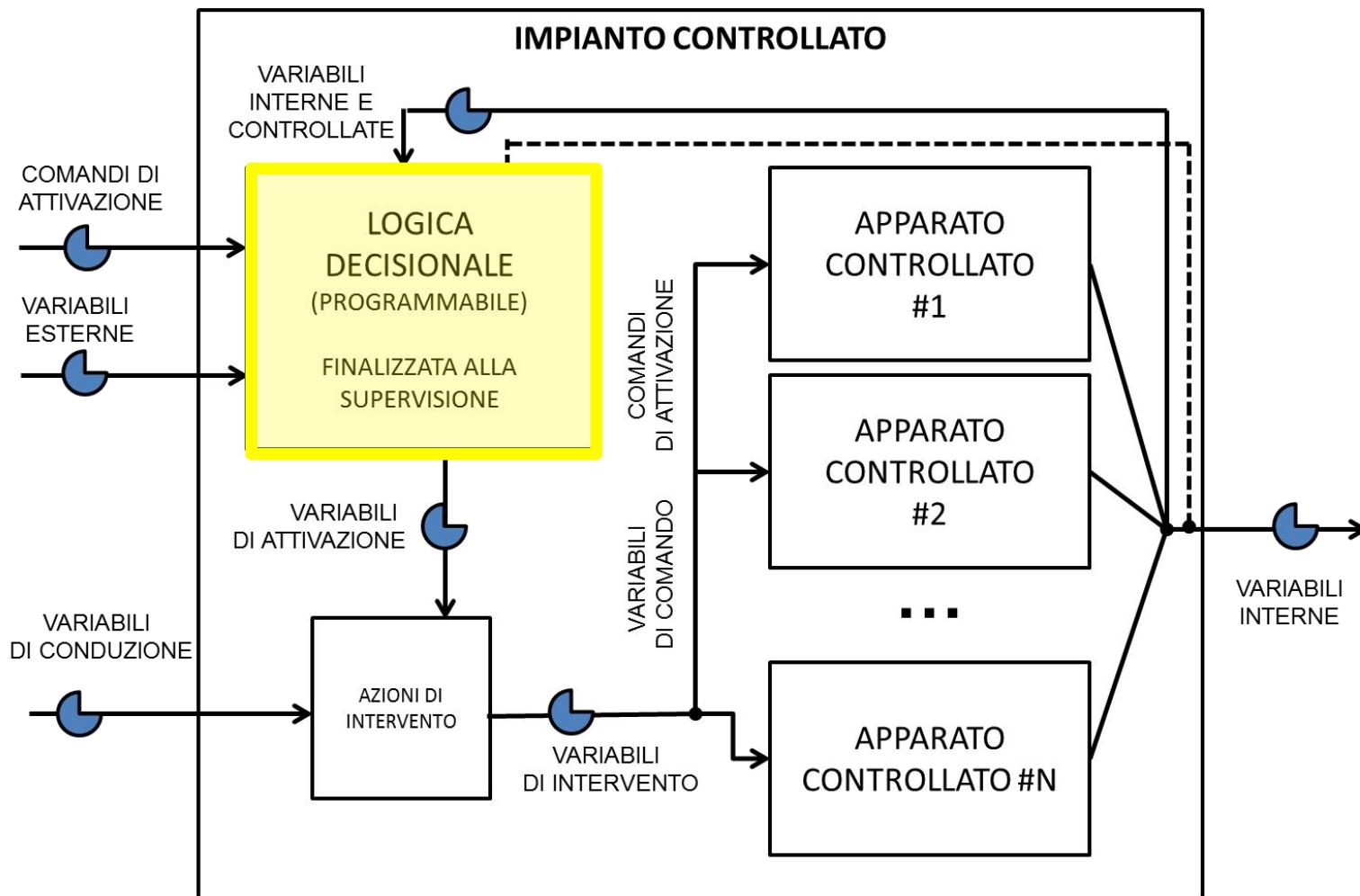

## APPLICAZIONE

Prima della applicazione delle azioni di intervento al sistema da controllare bisogna verificare che sussistano tutte le **CONDIZIONI CHE ASSICURINO IL CORRETTO FUNZIONAMENTO** e il corretto impiego del sistema controllato.

- La verifica viene effettuata sulle **VARIABILI DI CONSENSO**:

- Comandi di attivazione

- Variabili controllate

- Variabili interne

- Variabili esterne

- Sulla base delle informazioni ricevute, il programma deve fornire come risultato la decisione sotto forma di **VARIABILI DI INTERVENTO**.

# RETI LOGICHE

## RETI LOGICHE

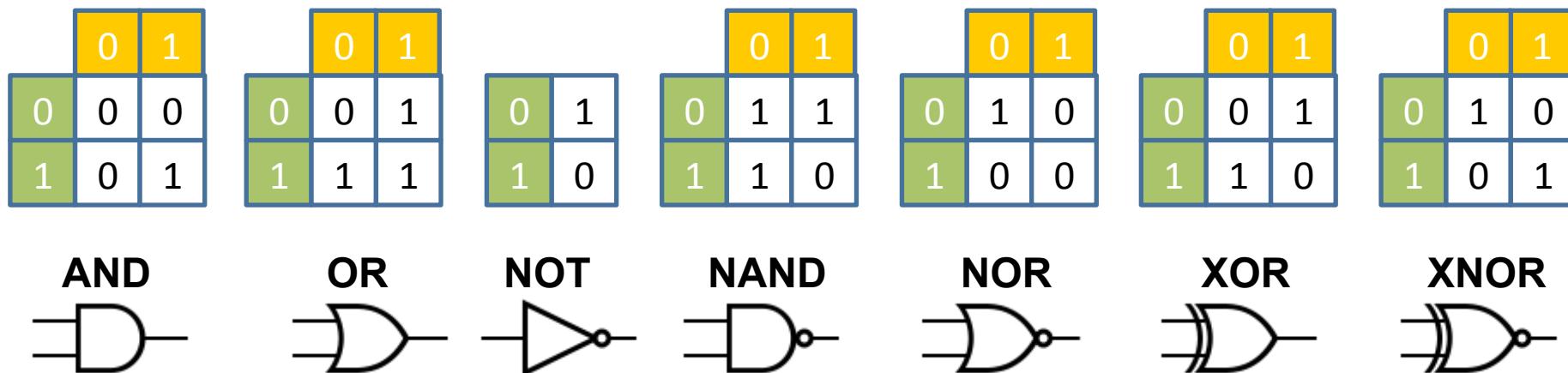

- le **reti logiche** sono **circuiti di elaborazione di tipo digitale** realizzati con **circuiti elettronici** che svolgono funzioni di tipo logico (AND, OR, NOT, NAND, NOR, XOR, XNOR)

- caratterizzati dal fatto che **in ogni istante i valori delle variabili di uscita dipendono dai valori delle variabili di ingresso e/o di alcune variabili di configurazione**

## CLASSIFICAZIONE DELLE RETI LOGICHE

Le reti logiche sono classificate in:

- **RETI COMBINATORIE**, quando ad ogni istante  $t$  le variabili di uscita sono funzioni solo delle variabili di ingresso presenti nello **stesso istante  $t$**

$$y(t) = f[u(t)] \quad \forall t \in \mathbb{R}$$

- **RETI SEQUENZIALI**, quando le variabili di uscita ad un certo istante  $t$  dipendono sia dalle variabili di ingresso allo stesso istante  $t$  sia dalle variabili di ingresso **fino all'istante  $t$**

$$y(t) = f[u(t'), \forall t' \leq t] \quad \forall t \in \mathbb{R}$$

## CLASSIFICAZIONE DELLE RETI LOGICHE

Le reti logiche sono classificate in:

- **RETI SINCRONE**, quando l'elaborazione avviene ad istanti **discreti**, stabiliti dal **clock** di sistema

- **RETI ASINCRONE**, quando l'elaborazione avviene a **flusso continuo**, ovvero il simbolo d'uscita si modifica quando si verifica una modifica del simbolo d'ingresso

## RETI LOGICHE

- Per tutte le variabili coinvolte nelle elaborazioni, i valori da prendere in considerazione sono sempre e solo quelli che vengono raggiunti **DOPO CHE SI È ESAURITO IL TRANSITORIO**

- La **contemporaneità** fra l'applicazione delle variabili di ingresso e la disponibilità delle variabili di uscita **in una rete logica combinatoria è solo teorica** in quanto tutte le elaborazioni richiedono un intervallo di tempo finito per l'esecuzione e tutti i circuiti presentano un transitorio

- Quando tale **TRANSITORIO È TRASCURABILE** rispetto al comportamento dinamico del sistema da controllare, le reti logiche combinatorie possono essere considerate **RETI ISTANTANEE**

# PLC

## DEFINIZIONE DI PLC - NORME IEC 61131.3

- il PLC è un **sistema elettronico a funzionamento digitale**

- destinato all'uso in **ambito industriale**

- utilizza una **memoria programmabile** per l'**archiviazione** interna di istruzioni orientate all'utilizzatore

- implementazione di funzioni **logiche**, di **sequenziamento**, di **temporizzazione**, di **conteggio** e **calcolo aritmetico**

- **controlla**, mediante ingressi ed uscite sia digitali che analogici, vari tipi di sistemi semplici e/o complessi

-

## CARATTERISTICHE DI UN PLC

Il PLC è un controllore con **architettura general-purpose** dedicata alle elaborazioni di tipo logico e idonea ad un ambiente industriale.

Le principali caratteristiche:

- **affidabilità** (ad es. 24/7, ridondanza x3, sicurezza certificata)

- **espandibilità** (sostituzione/aggiunta nel rack di moduli)

- **semplicità di programmazione** (tool sdk + gui, manuali)

- **riusabilità della logica di programma** (linguaggi standard)

- **interoperabilità tra dispositivi** di produttori diversi (i/f hw e sw)

## CONFRONTO FRA RETI LOGICHE E PLC

Le reti logiche possono essere realizzate con relè elettromeccanici oppure con circuiti elettronici a larga integrazione

### PRINCIPALI SVANTAGGI DELLE RETI LOGICHE

- elaborazione di **FUNZIONI LOGICHE DEFINITE RIGIDAMENTE** e collegate al tipo di contatto del relè o allo stato di conduzione dei circuiti elettronici nonché al cablaggio o alla realizzazione del circuito

- **PROGRAMMAZIONE RIGIDA** in quanto ogni modifica del programma comporta modifiche al cablaggio o alla struttura del circuito

- affidabilità dipendente da componenti **ELETTROMECCANICI** o dai **CIRCUITI ELETTRONICI**

- **CONNESSIONI** ai dispositivi di misura e agli attuatori **INGOMBRANTI**, difficili da realizzare e gestire

- **GUASTI** e manomissioni **DIFFICILI DA INDIVIDUARE**

## CONFRONTO FRA RETI LOGICHE E PLC

I PLC hanno le seguenti caratteristiche:

- sono utilizzati per ottenere lo **STESO COMPORTAMENTO** ingresso-uscita di una **rete logica**

- le singole elaborazioni sono eseguite secondo un programma **SERIALE**, istruzione dopo istruzione

- il limite di applicabilità è dato dalla **DURATA DEL TEMPO DI ELABORAZIONE** ed ai **VINCOLI TEMPORALI** imposti dalla necessità di una corretta applicazione dell'azione di controllo

## REALIZZAZIONE – RETI LOGICHE

- Le reti logiche vengono oggigiorno realizzate attraverso:

- **FPGA** (Field Programming Gate Array)

- **ASIC** (Application Specific Integrated Circuit)

## REALIZZAZIONE – PLC

- Dal punto di vista costruttivo i PLC sono classificati nella maniera seguente:

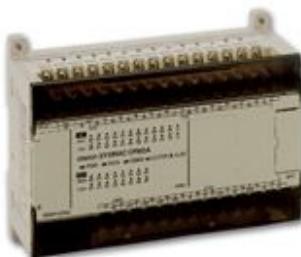

- **μPLC**, quando gli **ingressi e le uscite** sono tutte digitali e **inferiori a 64** e la **memoria inferiore a 2 kbyte**

- **PLC** di medie dimensioni, quando gli **ingressi e le uscite** possono essere **digitali e analogiche**, in numero **inferiore a 512** e la memoria dell'ordine di **decine di kbyte**

- **PLC** di grandi dimensioni, quando i predetti limiti sono superati

- I **μPLC** sono monoblocco, gli altri componibili a moduli secondo le esigenze

μPLC

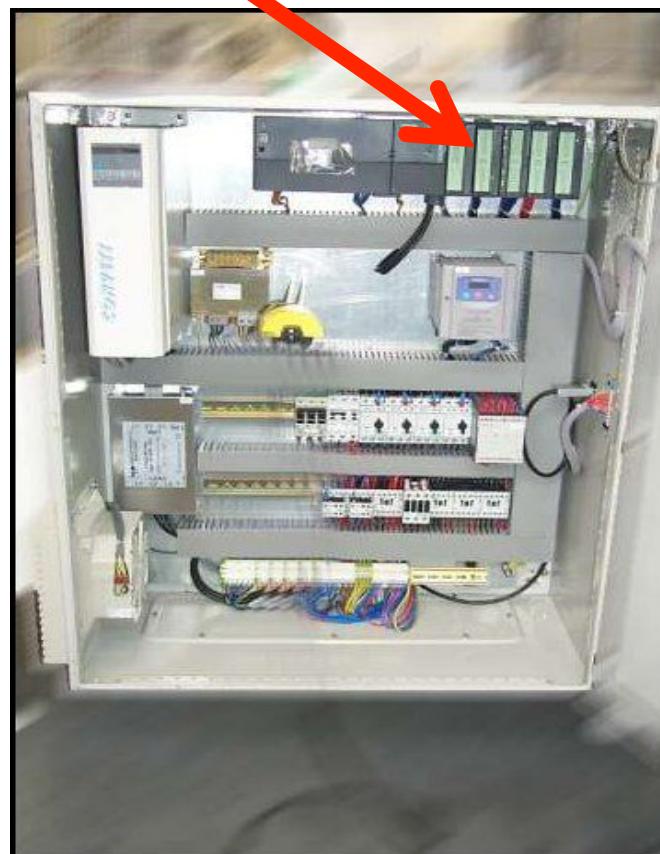

PLC MEDI

PLC GRANDI

STRUTTURA

MODULARE

DI UN PLC

## ESEMPIO DI INSERIMENTO DI UN PLC IN UN RACK

# STRUTTURA DEI PLC

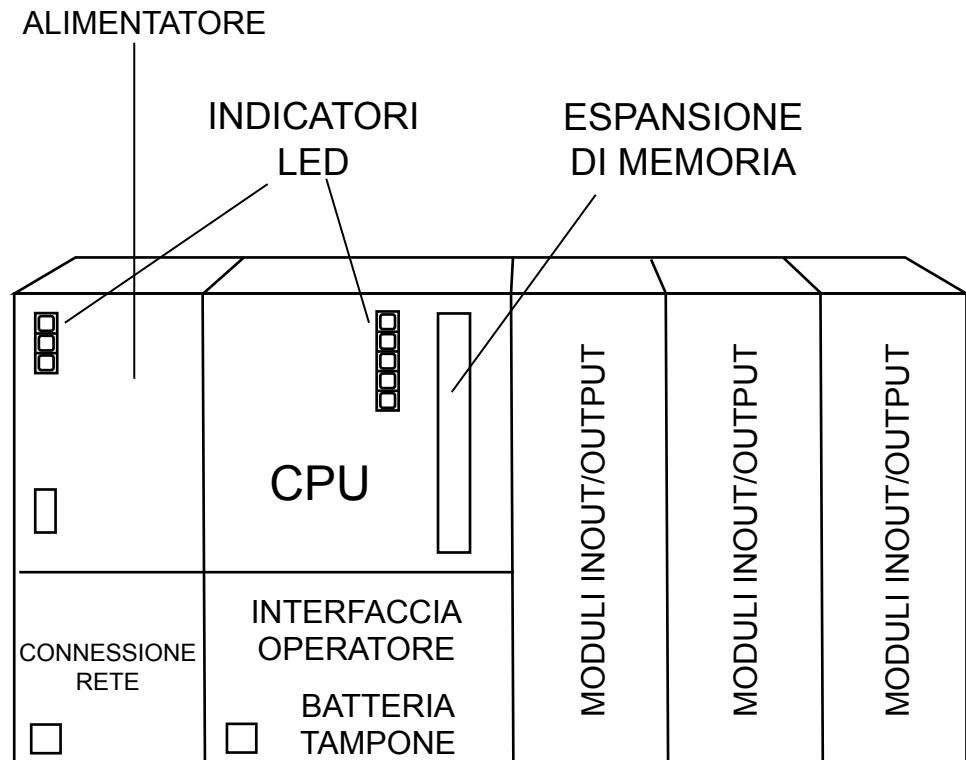

## ASPETTO FISICO DI UN PLC

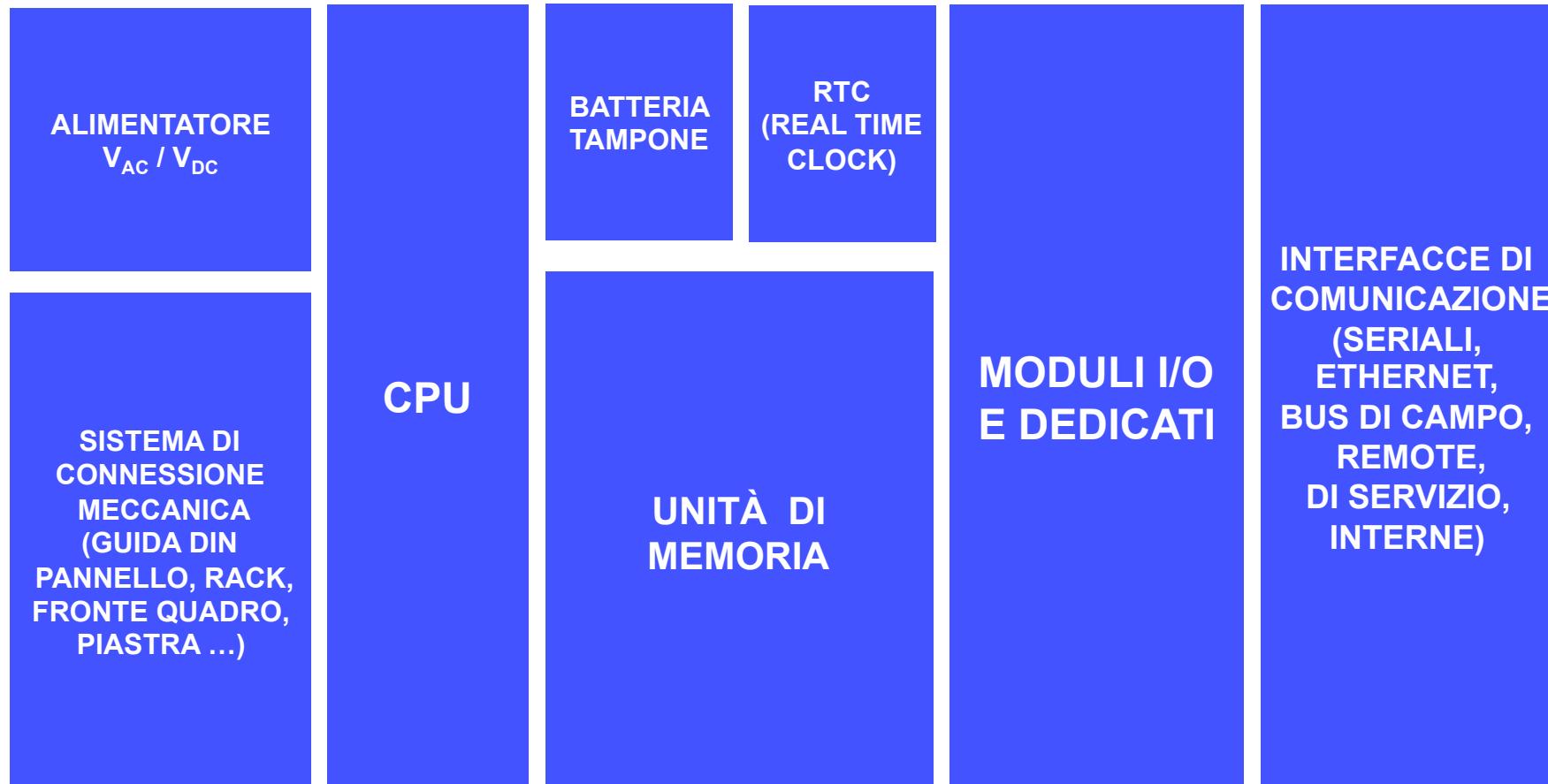

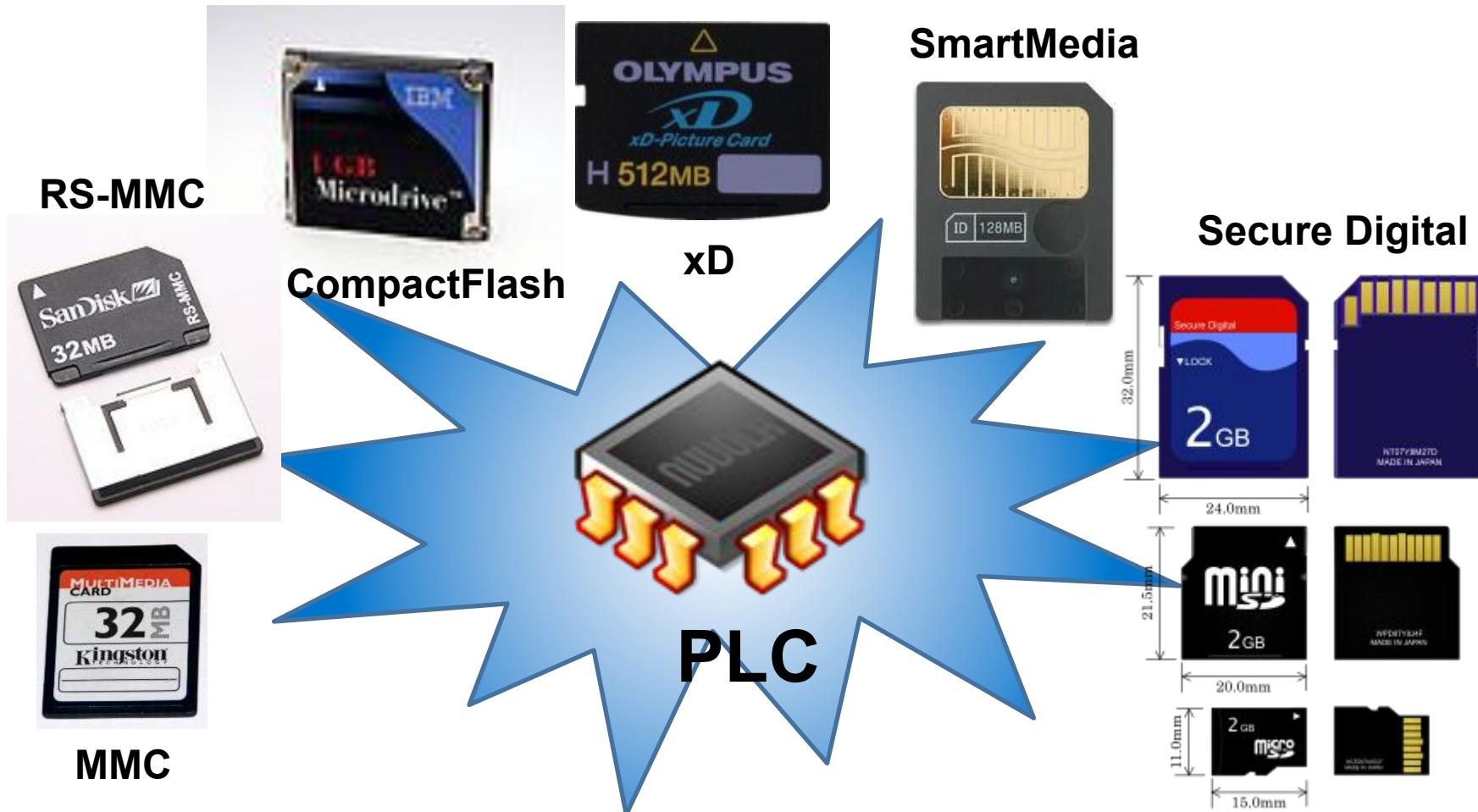

## SCHEMA A BLOCCHI FUNZIONALI DI UN PLC

## SEZIONE DI ALIMENTAZIONE

- interfacciamento con i sensori adattato alle possibili caratteristiche del segnale di uscita, che può essere:

- DC 5 - 12 - 24 – 48 V

- AC 110 – 280 V

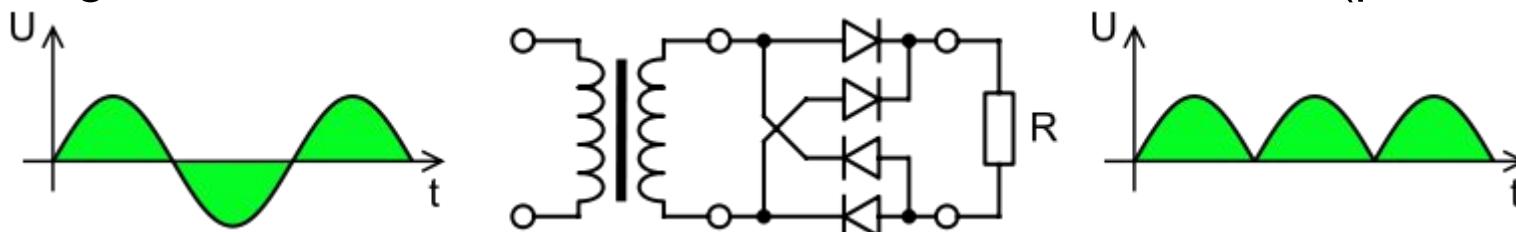

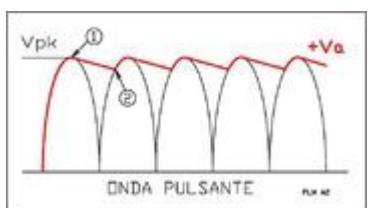

- per i segnali in alternata occorre uno stadio di **rettificazione** (ponte a diodi)

- e uno stadio di **livellamento** (condensatori elettrolitici di livellamento)

## SEZIONE DI INGRESSO

Gli elementi utilizzati per un efficace interfacciamento con il sistema da controllare sono:

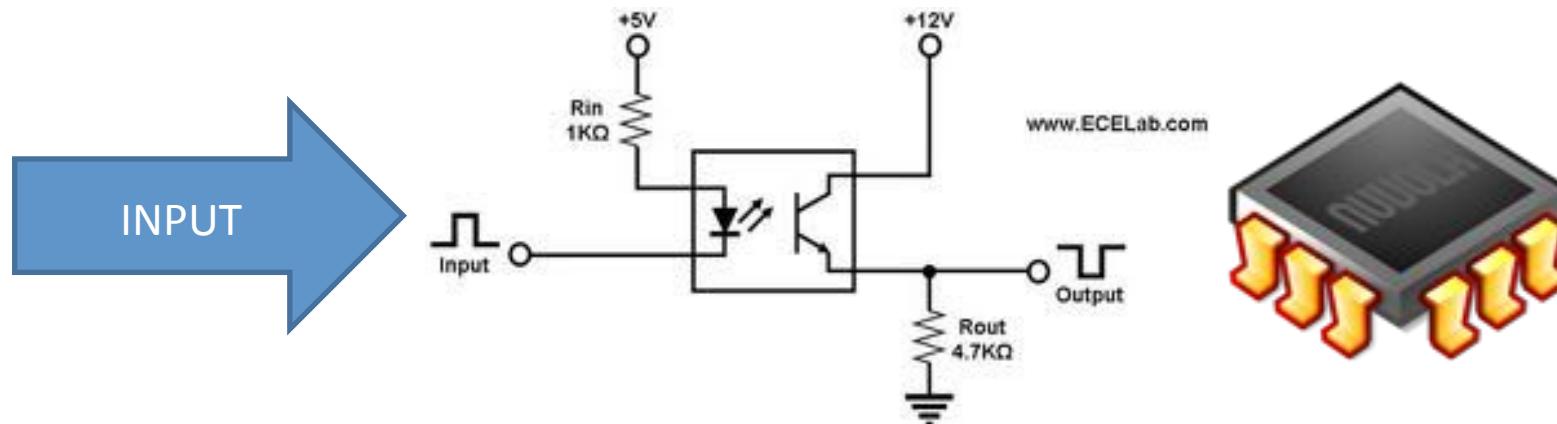

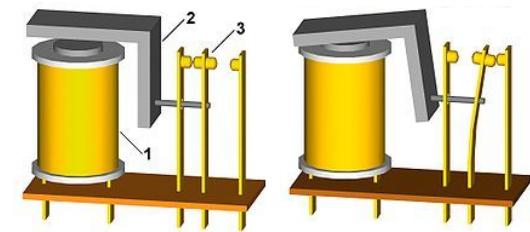

- stadio di isolamento realizzato in genere con **optoisolatori**

- utilizzazione di **contatti a vite** per velocizzare le procedure di installazione dei moduli

- visualizzazione dello stato per il **debug** del programma di elaborazione (ad es. tramite l'uso di **LED**)

## SEZIONE DI USCITA

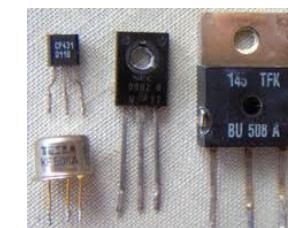

- **Relè** - componente elettromeccanico a solenoide, che permette di gestire elevate potenze con piccoli segnali di comando

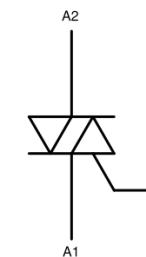

- **Triac** - è un relè allo stato solido che permette di gestire elevate potenze con piccoli segnali di comando e con limitata dissipazione di calore

- **Transistor** – componente elettronico per amplificazione di piccoli segnali

# STRUTTURA DEI PLC MEMORIA

## ORGANIZZAZIONE DELLA MEMORIA NEI PLC

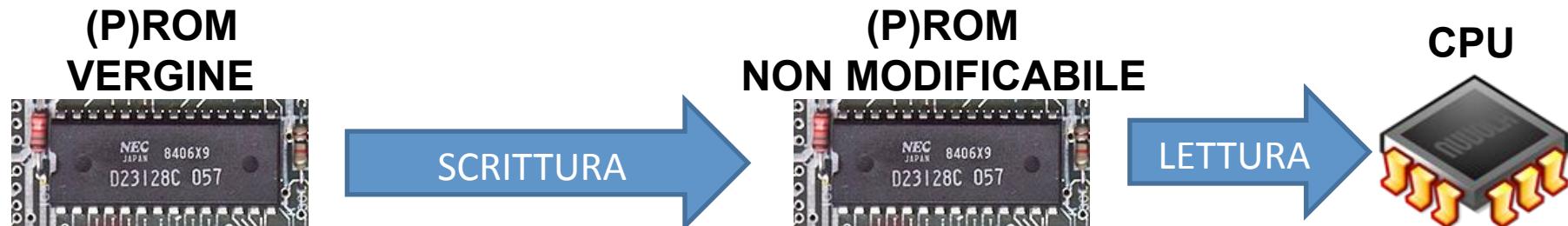

La memoria di un PLC è suddivisa in memoria **ROM** e memoria **RAM**

- memoria ROM (Read Only Memory) o PROM (Programmable ROM) di sola lettura in cui risiede il **sistema operativo** (Basic I/O System - BIOS)

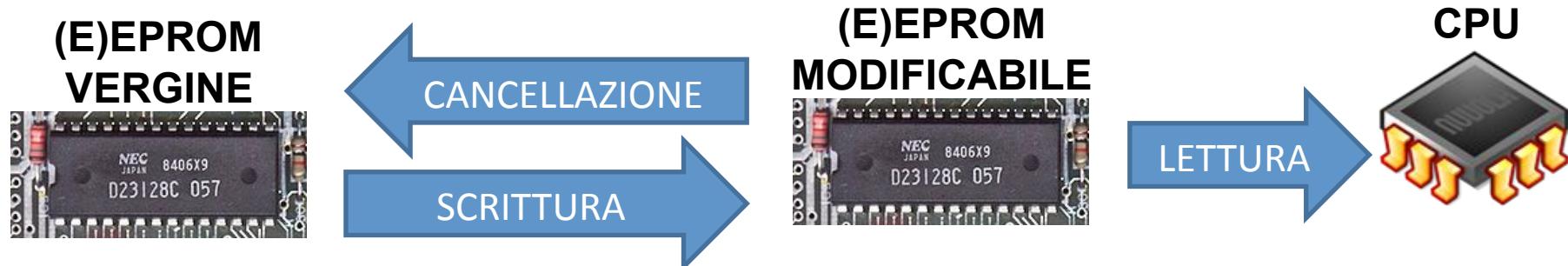

- memoria EPROM (Erasable Programmable ROM), EEPROM (Elettrically EPROM) per contenere il **programma da elaborare**, eventuali costanti e parametri

## ORGANIZZAZIONE DELLA MEMORIA NEI PLC

- Memoria RAM (Random Access Memory) per memorizzare il valore attuale delle variabili e alcune parti del programma scritto in (E)EPROM (caching)

## ORGANIZZAZIONE DELLA MEMORIA NEI PLC

### TIPOLOGIE DI MEMORIE RAM (RANDOM ACCESS MEMORY)

- La memoria RAM può essere letta e **scritta a blocchi** e non necessariamente in serie come la EEPROM.

- La memoria **SRAM** (Static RAM) **una volta scritta entra in idle** e non richiede ulteriore alimentazione. Ma se non alimentata può perdere le informazioni immagazzinate pertanto NON è come una EEPROM. E' **molto veloce, consuma poco**, di semplice progettazione ma di bassa densità e quindi di **alto costo per Mbyte**.

- La memoria **DRAM** (Dynamic RAM) viene **alimentata periodicamente** per evitare la perdita di dati. E' discretamente veloce, è energivora, ma ha una **densità altissima** e quindi meno costosa per Mbyte della SRAM.

## ORGANIZZAZIONE DELLA MEMORIA NEI PLC

- Le memorie **SRAM** sono **molto veloci, consumano poco**, ma sono **costose** pertanto sono solitamente usate per le **memorie cache**, dove elevate velocità e ridotti consumi sono le caratteristiche fondamentali.

- **Async SRAM** (SRAM asincrona) sono memorie che lavorano in modo **asincrono rispetto al clock della CPU** e ciò comporta stati di attesa della CPU (wait state) per l'accesso. Vengono utilizzate come **cache di secondo livello**.

- **Sync SRAM** (SRAM sincrona) sono memorie che lavorano in **sincronia con il clock della CPU** e hanno quindi tempi di attesa trascurabili. Vengono utilizzata come **cache di primo livello**.

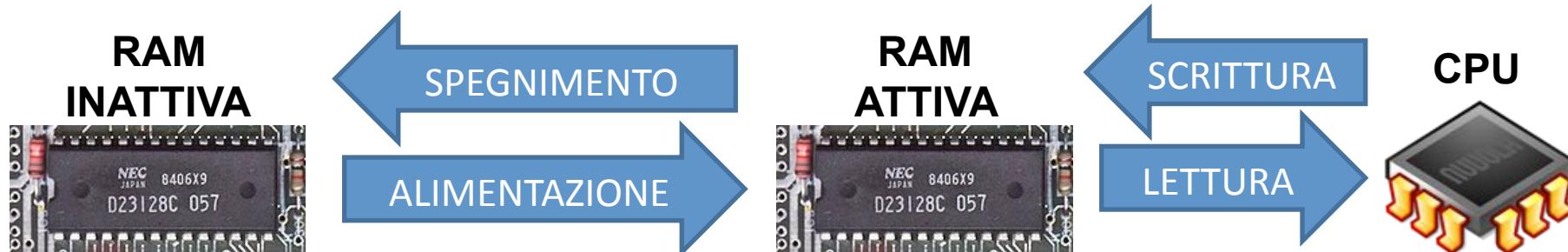

# MEMORIE EEPROM RIMOVIBILI

# STRUTTURA DEI PLC

## SEZIONE DI I/O

## SEZIONE DI INGRESSO/USCITA

Le schede input/output specializzate sono:

- **regolatori** standard PI+D

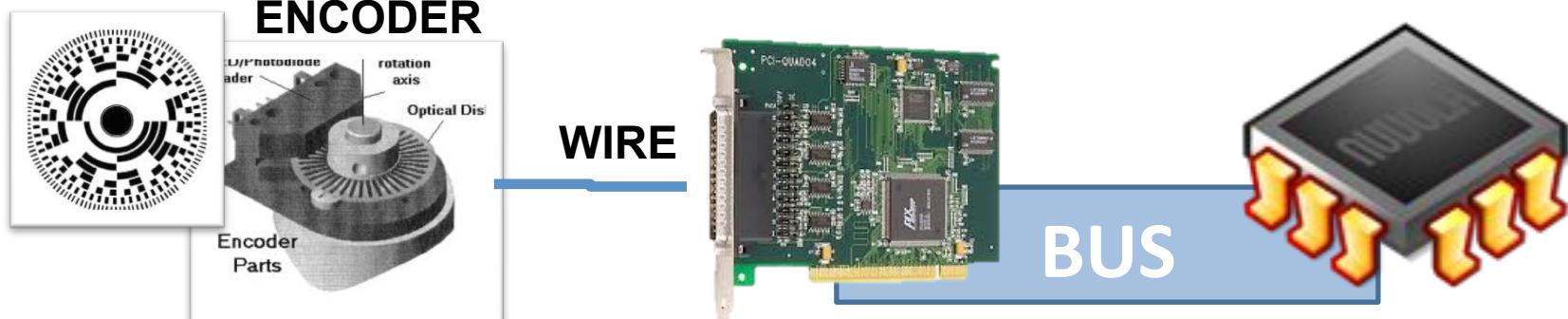

- schede per il **conteggio veloce** (lettura dell'uscita di un **encoder**)

- schede per la lettura e il controllo della **temperatura**

- schede di lettura degli **estensimetri**

- schede per il **controllo assi** - le schede controllo assi hanno la peculiarità che gli algoritmi da rendere operativi per realizzare una buona modalità di impiego del motore controllato sono in genere **sofisticati** e devono essere eseguiti con un **elevato passo di campionamento** e spesso hanno una **CPU dedicata**

## SCHEDE DI INGRESSO ANALOGICHE

- molti produttori di PLC rendono disponibili schede con ingressi analogici

- **Termoresistenze Pt100/Pt1000**

EFFETTO Seebeck

CHROMEL

ALUMEN

$$\rho(T) = \rho_0 \cdot [1 + \alpha(T - T_0)]$$

termo-resistenze

in platino (Pt),

in cui la resistenza alla

temperatura di 0 °C

è pari rispettivamente

a 100 Ω e 1000 Ω

• **Termocoppe T, J, K, ecc.**

ECONOMICHE

NON LINEARI

POCO ACCURATE (+/- 1°C)

RAME COSTANTANA      FERRO COSTANTANA

- queste schede sono disponibili con varie **risoluzioni** (8-12-16 bit) e con 1 o più ( $2^N$ ) ingressi distinti disponibili in morsettiera o con connettore

## SCHEDE DI COMUNICAZIONE

- il PLC durante il suo funzionamento può comunicare con altri PLC, computer o dispositivi CNC (**Computer Numerical Control**) come presse piegatrici, punzonatrici, torni, fresatrici e macchine di taglio lamiera

- la **comunicazione con computer** e altri dispositivi avviene tramite tipi di connessione standard come

- RS232 – Seriale

Recommended Standard

- RS422/RS485 – Seriale

Recommended Standard

- TCP/IP (RJ45) o USB

- la **comunicazione con altri PLC** avviene tramite protocolli standard, ad esempio:

- Profibus - Modbus - CANBUS – ecc.

## SCHEDE DI CONTEGGIO

- accolgono il segnale di un **sensore di conteggio e direzione** più un canale di **azzeramento**; il cablaggio funziona sia in **single ended** (Ground + Segnale, come nella RS232, non robusto al rumore) sia in **differenziale** (normalmente secondo lo standard RS-422)

DISCO

OTTICO

A 8 BIT

- normalmente è possibile programmarle in modo che scatenino un evento (per esempio alzando un'uscita) al raggiungimento di una **soglia** o all'interno di un **intervallo** di valori

## SCHEDE PI+D

- sono schede ad **un ingresso ed una uscita** ed applicano un anello di controllazione locale

utili per regolare temperature, pressioni, tensioni, correnti, etc.

# PROGRAMMAZIONE DEI PLC

# **SOFTWARE DI PROGRAMMAZIONE DEI PLC**

## **SECONDO LE NORME IEC 61131-3**

### **LINGUAGGI GRAFICI**

**LD**      **LADDER DIAGRAM**

**FBD**      **FUNCTIONAL BLOCK DIAGRAM**

**SCF**      **SEQUENTIAL FUNCTION CHART**

### **LINGUAGGI TESTUALI**

**IL**      **INSTRUCTION LIST**

**ST**      **STRUCTURATED TEXT**

# LINGUAGGI DI PROGRAMMAZIONE

## SECONDO LE NORME IEC 61131

### LINGUAGGI DI PROGRAMMAZIONE GRAFICI

**LADDER DIAGRAM** ottenuto come **trasposizione** informatica dei **quadri a relè SCHEMA A CONTATTI**

**FUNCTIONAL BLOCK DIAGRAM** ottenuto come **trasposizione** dei **diagrammi circuitali** in cui le interconnessioni rappresentano i **percorsi dei segnali** che collegano i vari componenti; i blocchi rappresentano le singole operazioni logiche

**SEQUENTIAL FUNCTIONAL CHART** ottenuto applicando un formalismo grafico per la descrizione di **operazioni logiche sequenziali** e formalismi grafici proprio di altri linguaggi di programmazione; utilizzato per descrivere in maniera orientata alla **progettazione sistemi complessi di automazione**

# LINGUAGGI DI PROGRAMMAZIONE

## SECONDO LE NORME IEC 61131

### LINGUAGGI DI PROGRAMMAZIONE TESTUALI

#### INSTRUCTION LIST

linguaggio di programmazione di **basso livello** molto simile all'**ASSEMBLER**; le istruzioni sono costituite da un operatore e da un solo operando e fanno riferimento ad un registro di memoria; i formalismi adottati possono essere molto differenti in quanto fissati dal produttore dell'hardware per il PLC

#### STRUCTURED TEXT

linguaggio di programmazione strutturato ad **alto livello** con un formalismo che si ispira al **BASIC** e al **PASCAL**; è adatto alla rappresentazione di procedure complesse che non potrebbero essere descritte con i linguaggi grafici